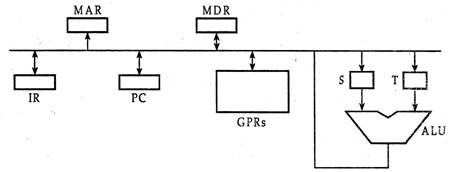

考虑CPU的以下数据路径。

null

数据路径中的、ALU、总线和所有寄存器的大小相同。所有操作,包括PC和GPRs的增量,都将在ALU中执行。内存读取操作需要两个时钟周期——第一个用于在MAR中加载地址,第二个用于将数据从内存总线加载到MDR

指令“add R0,R1”具有寄存器传输解释R0<=R0+R1。此指令的执行周期所需的最小时钟周期数为。 (A) 2. (B) 3. (C) 4. (D) 5. 答复: (B) 说明:

从图中可以清楚地看出,在ALU执行任何操作之前,必须将操作数加载到S&T寄存器中。将操作数从R移到 0 & R 1. 对于S&T,需要两个时钟周期。此外,ALU和寄存器的大小相同,因此操作可以在一个只需要一个时钟周期的单级中执行(如果操作数的大小大于ALU,则操作数被拆分,操作分阶段执行)。

1) S<=R 0 :从R移动操作数 0 去登记。 2) T<=R 1. :从R移动操作数 1. 去登记。 3) R 0 <=S+T:将操作数相加并存储回R中 0

因此,执行阶段需要3个时钟周期。

© 版权声明

文章版权归作者所有,未经允许请勿转载。

THE END

![关于”PostgreSQL错误:关系[表]不存在“问题的原因和解决方案-yiteyi-C++库](https://www.yiteyi.com/wp-content/themes/zibll/img/thumbnail.svg)